# digital

## DIGITAL Semiconductor 21140A PCI Fast Ethernet LAN Controller

## Hardware Reference Manual

Order Number: EC-QN7NF-TE

**Revision/Update Information:** This is a revised document. It supersedes the DIGITAL Semiconductor 21140A PCI Fast Ethernet LAN Controller Hardware Reference Manual, EC–QN7NE–TE.

Digital Equipment Corporation Maynard, Massachusetts

http://www.digital.com/semiconductor

## **Important Notice**

As of May 17, 1998, Digital Equipment Corporation's StrongARM, PCI Bridge, and Networking component businesses, along with the chip fabrication facility in Hudson, Massachusetts, were acquired by Intel Corporation and transferred to Intel Massachusetts, Inc. As a result of this transaction, certain references to web sites, telephone numbers, and fax numbers have changed in the documentation. This information will be updated in the next version of this manual. Copies of documents that have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling **1-800-332-2717** or by visiting Intel's website for developers at:

#### http://developer.intel.com

The Intel Massachusetts Customer Technology Center continues to service your StrongARM Product, Bridge Product, and Network Product technical inquiries. Please use the following information lines for support:

| For documentation and general informa                                    | tion:                               |  |

|--------------------------------------------------------------------------|-------------------------------------|--|

| Intel Massachusetts Information Line                                     |                                     |  |

| United States:                                                           | 1-800-332-2717                      |  |

| Outside United States:                                                   | 1-303-675-2148                      |  |

| Electronic mail address:                                                 | techdoc@intel.com                   |  |

|                                                                          |                                     |  |

| For technical support:                                                   |                                     |  |

|                                                                          |                                     |  |

| Intel Massachusetts Customer Technolo                                    | ogy Center                          |  |

| Intel Massachusetts Customer Technolo<br>Phone (U.S. and international): | <b>Dgy Center</b><br>1–978–568–7474 |  |

|                                                                          |                                     |  |

#### March 1998

While DIGITAL believes the information included in this publication is correct as of the date of publication, it is subject to change without notice.

Please read the Support, Products, and Documentation section in this document to determine how to obtain current product update and errata information.

Digital Equipment Corporation makes no representations that the use of its products in the manner described in this publication will not infringe on existing or future patent rights, nor do the descriptions contained in this publication imply the granting of licenses to make, use, or sell equipment or software in accordance with the description.

©Digital Equipment Corporation 1998. All rights reserved. Printed in U.S.A.

DIGITAL, DIGITAL Semiconductor, DNA, and the DIGITAL logo are trademarks of Digital Equipment Corporation.

DIGITAL Semiconductor is a Digital Equipment Corporation business.

IEEE is a registered trademark of The Institute of Electrical and Electronics Engineers, Inc. MicroWire is a registered trademark of BankAmerica Corporation.

All other trademarks and registered trademarks are the property of their respective owners.

# Contents

### Preface

### 1 Introduction

| 1.1 | General Description | 1–1 |

|-----|---------------------|-----|

|     | 21140A Features     |     |

| 1.2 | Hardware Overview   | 1–3 |

## 2 Signal Descriptions

| 2.1 | 21140A Pinout       | 2–1 |

|-----|---------------------|-----|

| 2.2 | Signal Descriptions | 2–3 |

## 3 Registers

| 3.1      | Configuration Operation                                         | 3–1  |

|----------|-----------------------------------------------------------------|------|

| 3.1.1    | Configuration Register Mapping                                  | 3–2  |

| 3.1.2    | Configuration Registers                                         | 3–2  |

| 3.1.2.1  | Configuration ID Register (CFID–Offset 00H)                     | 3–2  |

| 3.1.2.2  | Command and Status Configuration Register (CFCS–Offset 04H)     | 3–3  |

| 3.1.2.3  | Configuration Revision Register (CFRV–Offset 08H)               | 3–6  |

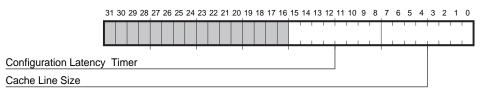

| 3.1.2.4  | Configuration Latency Timer Register (CFLT–Offset 0CH)          | 3–8  |

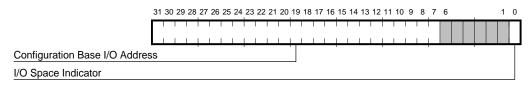

| 3.1.2.5  | Configuration Base I/O Address Register (CBIO—Offset 10H)       | 3–10 |

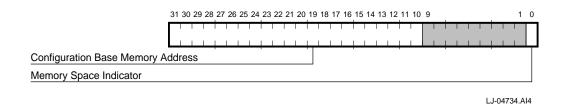

| 3.1.2.6  | Configuration Base Memory Address Register (CBMA–Offset 14H)    | 3–11 |

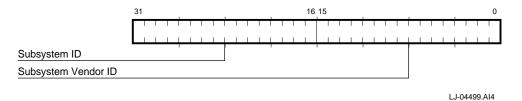

| 3.1.2.7  | Subsystem ID Register (SSID–Offset 2CH)                         | 3–12 |

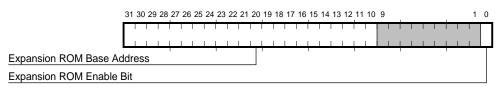

| 3.1.2.8  | Expansion ROM Base Address Register (CBER–Offset 30H)           | 3–13 |

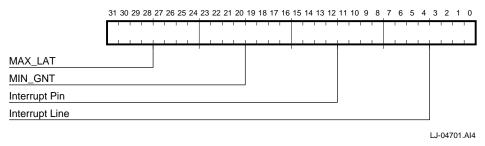

| 3.1.2.9  | Configuration Interrupt Register (CFIT–Offset 3CH)              | 3–14 |

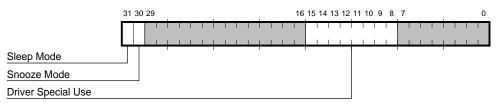

| 3.1.2.10 | Configuration Device and Driver Area Register (CFDD–Offset 40H) | 3–15 |

| 3.2      | CSR Operation                                                   | 3–17 |

| 3.2.1    | Control and Status Register Mapping                             | 3–17 |

| 3.2.2    | Host CSRs                                                       | 3–18 |

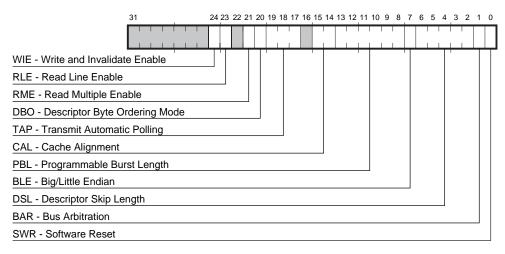

| 3.2.2.1  | Bus Mode Register (CSR0–Offset 00H)                      | 3–18 |

|----------|----------------------------------------------------------|------|

| 3.2.2.2  | Transmit Poll Demand Register (CSR1–Offset 08H)          | 3–22 |

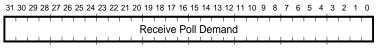

| 3.2.2.3  | Receive Poll Demand Register (CSR2–Offset 10H)           | 3–23 |

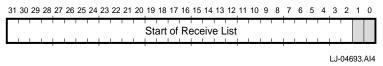

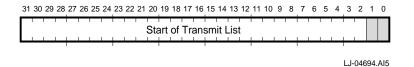

| 3.2.2.4  | Descriptor List Address Registers (CSR3–Offset 18H and   |      |

|          | CSR4–Offset 20H)                                         | 3–24 |

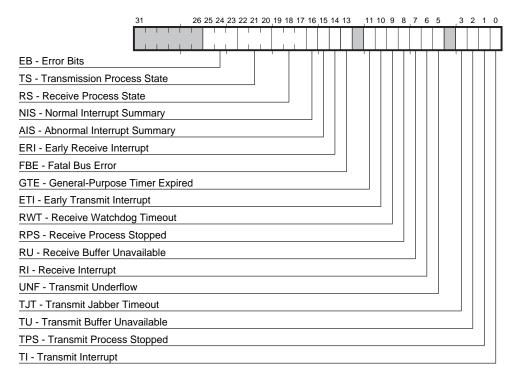

| 3.2.2.5  | Status Register (CSR5–Offset 28H)                        | 3–26 |

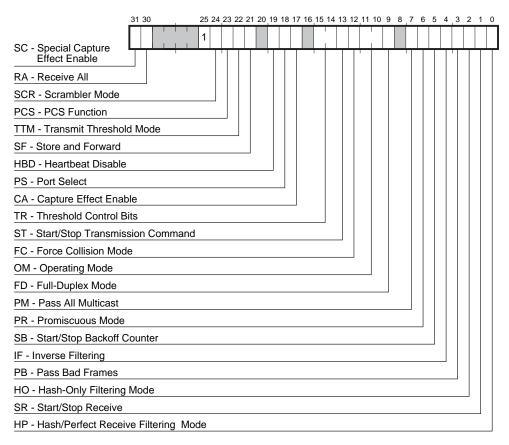

| 3.2.2.6  | Operation Mode Register (CSR6–Offset 30H)                | 3–31 |

| 3.2.2.7  | Interrupt Enable Register (CSR7–Offset 38H)              | 3–40 |

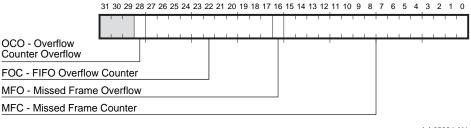

| 3.2.2.8  | Missed Frames and Overflow Counter (CSR8–Offset 40H)     | 3–44 |

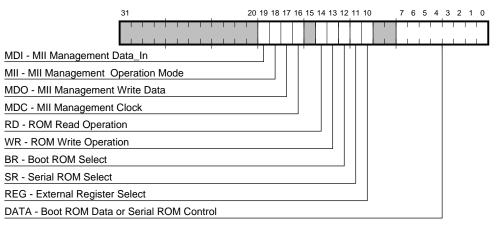

| 3.2.2.9  | Boot ROM, Serial ROM, and MII Management Register        |      |

|          | (CSR9–Offset 48H)                                        | 3–46 |

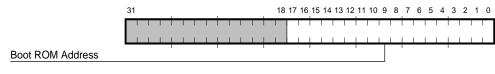

| 3.2.2.10 | Boot ROM Programming Address Register (CSR10–Offset 50H) | 3–48 |

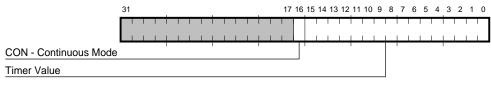

| 3.2.2.11 | General-Purpose Timer Register (CSR11–Offset 58H)        | 3–49 |

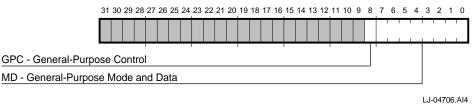

| 3.2.2.12 | General-Purpose Port Register (CSR12–Offset 60H)         | 3–50 |

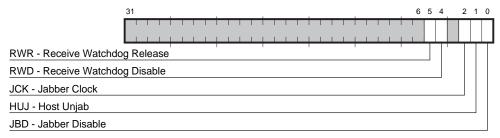

| 3.2.2.13 | Watchdog Timer Register (CSR1–Offset 78H)                | 3–52 |

|          |                                                          |      |

### 4 Host Communication

| 4.1     | Data Communication                     | 4–1  |

|---------|----------------------------------------|------|

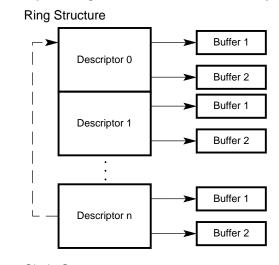

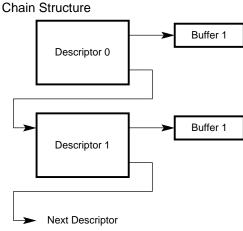

| 4.2     | Descriptor Lists and Data Buffers      | 4–1  |

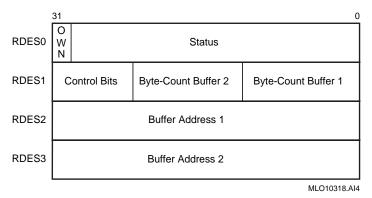

| 4.2.1   | Receive Descriptors                    | 4–3  |

| 4.2.1.1 | Receive Descriptor 0 (RDES0)           | 4–3  |

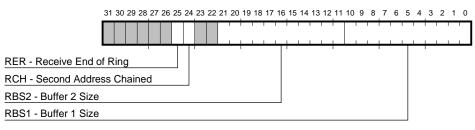

| 4.2.1.2 | Receive Descriptor 1 (RDES1)           | 4–8  |

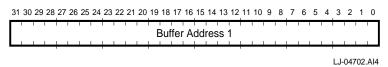

| 4.2.1.3 | Receive Descriptor 2 (RDES2)           | 4–9  |

| 4.2.1.4 | Receive Descriptor 3 (RDES3)           | 4–10 |

| 4.2.1.5 | Receive Descriptor Status Validity     | 4–10 |

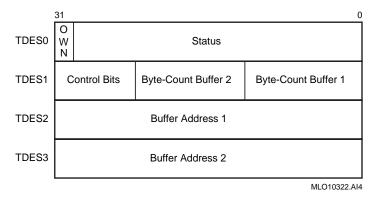

| 4.2.2   | Transmit Descriptors                   | 4–12 |

| 4.2.2.1 | Transmit Descriptor 0 (TDES0)          | 4–13 |

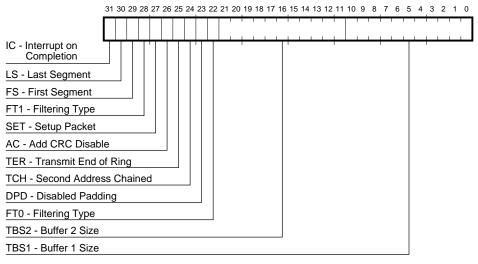

| 4.2.2.2 | Transmit Descriptor 1 (TDES1)          | 4–16 |

| 4.2.2.3 | Transmit Descriptor 2 (TDES2)          | 4–18 |

| 4.2.2.4 | Transmit Descriptor 3 (TDES3)          | 4–19 |

| 4.2.2.5 | Transmit Descriptor Status Validity    | 4–19 |

| 4.2.3   | Setup Frame                            | 4–20 |

| 4.2.3.1 | First Setup Frame                      | 4–21 |

| 4.2.3.2 | Subsequent Setup Frames                | 4–21 |

| 4.2.3.3 | Perfect Filtering Setup Frame Buffer   | 4–21 |

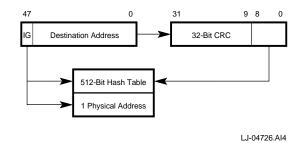

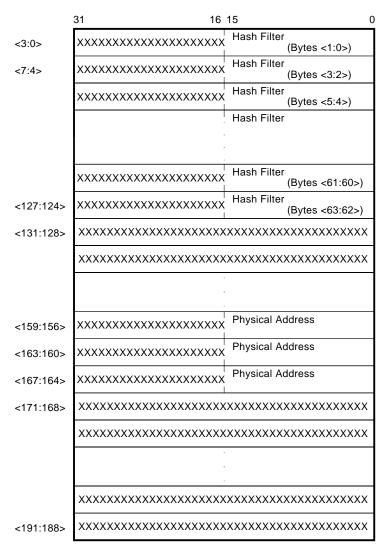

| 4.2.3.4 | Imperfect Filtering Setup Frame Buffer | 4–24 |

| 4.3     | Functional Description                 | 4–30 |

| 4.3.1   | Reset Commands                         | 4–30 |

| 4.3.2   | Arbitration Scheme                     | 4–31 |

| 4.3.3   | Interrupts                             | 4–33 |

| 4.3.4   | Startup Procedure                      | 4–34 |

| 4.3.5   | Receive Process                        | 4–35 |

| 4.3.5.1 | Descriptor Acquisition                 | 4–35 |

| 4.3.5.2 | Frame Processing                       | 4–35 |

|         |                                        |      |

| 4–36 |

|------|

| 4–36 |

|      |

| 4–37 |

| 4–37 |

| 4–38 |

| 4–39 |

|      |

## 5 Host Bus Operation

| 5.1       | Overview                                 | 5–1  |

|-----------|------------------------------------------|------|

| 5.2       | Bus Commands                             | 5–2  |

| 5.3       | Bus Slave Operation                      | 5–2  |

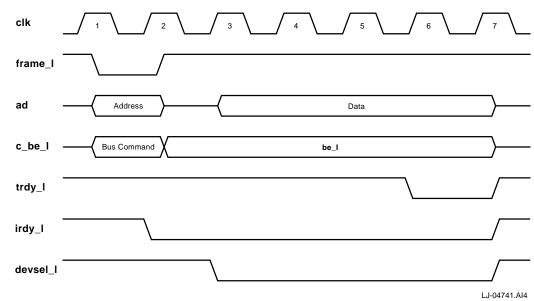

| 5.3.1     | Slave Read Cycle (I/O or Memory Target)  | 5–3  |

| 5.3.2     | Slave Write Cycle (I/O or Memory Target) | 5–4  |

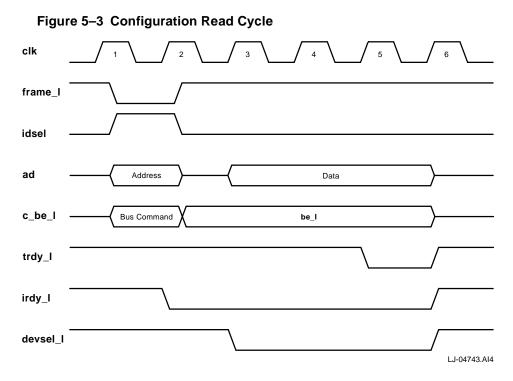

| 5.3.3     | Configuration Read and Write Cycles      | 5–5  |

| 5.4       | Bus Master Operation                     | 5–6  |

| 5.4.1     | Bus Arbitration                          | 5–6  |

| 5.4.2     | Memory Read Cycle                        | 5–7  |

| 5.4.3     | Memory Write Cycle                       | 5–8  |

| 5.5       | Termination Cycles                       | 5–9  |

| 5.5.1     | Slave-Initiated Termination              | 5–9  |

| 5.5.2     | Master-Initiated Termination             | 5–10 |

| 5.5.2.1   | 21140A-Initiated Termination             | 5–11 |

| 5.5.2.1.1 | Normal Completion                        | 5–11 |

| 5.5.2.1.2 | 2 Timeout                                | 5–11 |

| 5.5.2.1.3 | Master Abort                             | 5–11 |

| 5.5.2.2   | Memory-Controller-Initiated Termination  | 5–12 |

| 5.5.2.2.1 |                                          | 5–12 |

| 5.5.2.2.2 | Target Disconnect Termination            | 5–13 |

| 5.5.2.2.3 |                                          | 5–14 |

| 5.6       | Parity                                   | 5–15 |

| 5.7       | Parking                                  | 5–16 |

|           |                                          |      |

## 6 Network Interface Operation

| 6.1     | MII/SYM Port                   | 6–1 |

|---------|--------------------------------|-----|

| 6.1.1   | 100BASE-T Terminology          | 6–1 |

| 6.1.2   | Interface Description          | 6–2 |

| 6.1.2.1 | Signal Standards               | 6–3 |

| 6.1.2.2 | Operating Modes                | 6–4 |

| 6.2     | Serial Port                    | 6–6 |

| 6.3     | Media Access Control Operation | 6–6 |

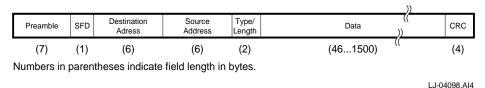

| 6.3.1   | MAC Frame Format               | 6–7 |

| 6.3.1.1 | Ethernet and IEEE 802.3 Frames | 6–8 |

| 6.3.1.2   | Ethernet Frame Format Description         | 6–8  |

|-----------|-------------------------------------------|------|

| 6.3.2     | Ethernet Reception Addressing             | 6–10 |

| 6.3.3     | Detailed Transmit Operation               | 6–11 |

| 6.3.3.1   | Transmit Initiation                       | 6–11 |

| 6.3.3.2   | Frame Encapsulation                       | 6–12 |

| 6.3.3.3   | Initial Deferral                          | 6–12 |

| 6.3.3.4   | Collision                                 | 6–13 |

| 6.3.3.5   | Terminating Transmission                  | 6–14 |

| 6.3.3.6   | Transmit Parameter Values                 | 6–14 |

| 6.3.4     | Detailed Receive Operation                | 6–15 |

| 6.3.4.1   | Receive Initiation                        | 6–15 |

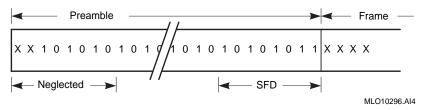

| 6.3.4.2   | Preamble Processing                       | 6–15 |

| 6.3.4.2.1 |                                           | 6–15 |

| 6.3.4.2.2 | 2 100BASE-TX or 100BASE-FX Mode Preambles | 6–16 |

| 6.3.4.3   | Address Matching                          | 6–17 |

| 6.3.4.4   | Frame Decapsulation                       | 6–17 |

| 6.3.4.5   | Terminating Reception                     | 6–17 |

| 6.3.4.6   | Frame Reception Status                    | 6–18 |

| 6.4       | Loopback Operations                       | 6–19 |

| 6.4.1     | Internal Loopback Mode                    | 6–19 |

| 6.4.2     | External Loopback Mode                    | 6–19 |

| 6.5       | Full-Duplex Operation                     | 6–19 |

| 6.6       | Capture Effect–A Value-Added Feature      | 6–20 |

| 6.6.1     | What Is Capture Effect?                   | 6–20 |

| 6.6.2     | Resolving Capture Effect                  | 6–22 |

| 6.6.3     | Enhanced Resolution for Capture Effect    | 6–22 |

| 6.7       | Power-Saving Modes                        | 6–22 |

| 6.7.1     | Sleep Power-Saving Mode                   | 6–23 |

| 6.7.2     | Snooze Power-Saving Mode                  | 6–23 |

| 6.8       | Jabber and Watchdog Timers                | 6–24 |

### 7 External Ports

| 7.1   | Overview                              | 7–1  |

|-------|---------------------------------------|------|

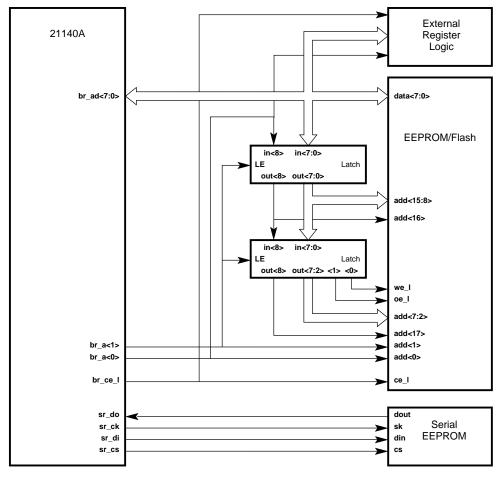

| 7.2   | Boot ROM and Serial ROM Connection    | 7–1  |

| 7.3   | Boot ROM Operations                   | 7–3  |

| 7.3.1 | Byte Read                             | 7–3  |

| 7.3.2 | Byte Write                            | 7–4  |

| 7.3.3 | Dword Read                            | 7–5  |

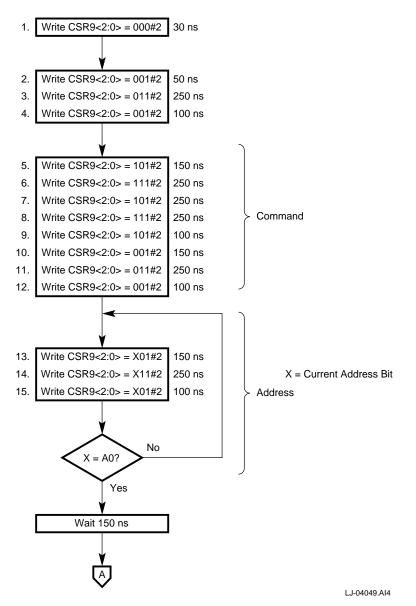

| 7.4   | Serial ROM Operations                 | 7–6  |

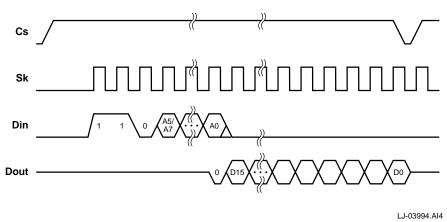

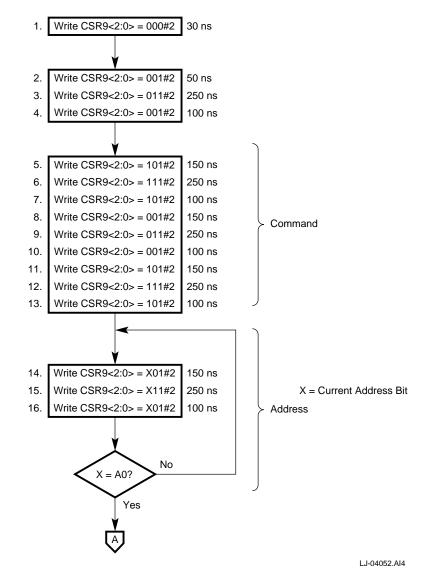

| 7.4.1 | Read Operation                        | 7–7  |

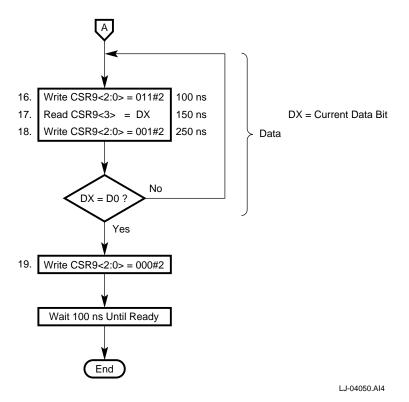

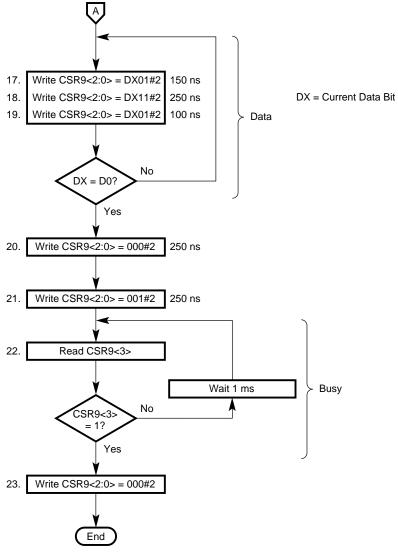

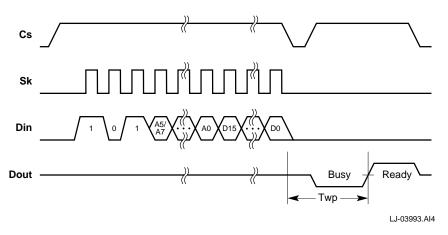

| 7.4.2 | Write Operation                       | 7–10 |

| 7.5   | External Register Operation           | 7–13 |

| 7.6   | General-Purpose Port Register (CSR12) | 7–14 |

| 7.7   | LED Support                           | 7–14 |

### A Joint Test Action Group—Test Logic

| A.1   | General Description         | A–1 |

|-------|-----------------------------|-----|

| A.2   | Registers                   | A–2 |

| A.2.1 | Instruction Register        | A–2 |

| A.2.2 | Bypass Register             | A–3 |

| A.2.3 | Boundary-Scan Register      | A-4 |

| A.2.4 | Test Access Port Controller | A–4 |

### B DNA CSMA/CD Counters and Events Support

### C Hash C Routine

D Support, Products, and Documentation

Index

### Examples

| 4–1 | Perfect Filtering Buffer   |  |

|-----|----------------------------|--|

| 4–2 | Imperfect Filtering Buffer |  |

## Figures

| 1–1            | 21140A Block Diagram                                   | 1–5        |

|----------------|--------------------------------------------------------|------------|

| 2–1            | 21140A Pinout Diagram (Top View)                       | 2–2        |

| 3–1            | CFID Configuration ID Register                         | 3–2        |

| 3–2            | CFCS Command and Status Configuration Register         | 3–4        |

| 3–3            | CFRV Configuration Revision Register                   | 3–7        |

| 3–4            | CFLT Configuration Latency Timer Register              | 3–8        |

| 3–5            | CBIO Configuration Base I/O Address Register           | 3–10       |

| 3–6            | CBMA Configuration Base Memory Address Register        | 3–11       |

| 3–7            | SSID Subsystem ID Register                             | 3–12       |

| 3–8            | CBER Expansion ROM Base Address Register               | 3–13       |

| 3–9            | CFIT Configuration Interrupt Register                  | 3–14       |

| 3–10           | CFDD Configuration Driver Area Register                | 3–15       |

| 3–11           | CSR0 Bus Mode Register                                 | 3–18       |

| 3–12           | CSR1 Transmit Poll Demand Register                     | 3–22       |

| 3–13           | CSR2 Receive Poll Demand Register                      | 3–23       |

| 3–14           | CSR3 Receive List Base Address Register                | 3–24       |

| 3–15           | CSR4 Transmit List Base Address Register               | 3-25       |

| 3–16           | CSR5 Status Register.                                  | 3–26       |

| 3–17           | CSR6 Operating Mode Register                           | 3-32       |

| 3–18           | CSR7 Interrupt Enable Register                         | 3–41       |

| 3–19           | CSR8 Missed Frames and Overflow Counter                | 3–45       |

| 3–20           | CSR9 Boot ROM, Serial ROM, and MII Management Register | 3–46       |

| 3–21           | CSR10 Boot ROM Programming Address Register            | 3–49       |

| 3–22           | CSR11 General-Purpose Timer Register                   | 3–50       |

| 3–23           | CSR12 General-Purpose Port Register                    | 3–51       |

| 3–24           | CSR15 Watchdog Timer Register.                         | 3–52       |

| 4-1            | Descriptor Ring and Chain Structure Examples           | 4-2        |

| 4–2            | Receive Descriptor Format                              | 4–3        |

| 4–3            | RDES0 Receive Descriptor 0                             | 4-4        |

| 4-4            | RDES1 Receive Descriptor 1                             | 4–8        |

| 4–5            | RDES2 Receive Descriptor 2                             | 4-9        |

| 4–6            | RDES3 Receive Descriptor 3                             | 4-10       |

| 4–7            | Transmit Descriptor Format                             | 4–12       |

| 4–8            | TDES0 Transmit Descriptor 0                            | 4–13       |

| 4-9            | TDES1 Transmit Descriptor 1                            | 4–16       |

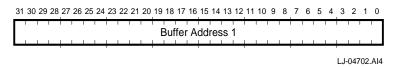

| 4–10           | TDES2 Transmit Descriptor 2                            | 4–19       |

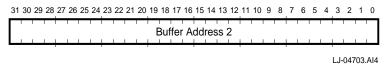

| 4–11           | TDES3 Transmit Descriptor 3                            | 4–19       |

| 4–12           | Perfect Filtering Setup Frame Buffer Format            | 4-22       |

| 4–13           | Imperfect Filtering                                    | 4-24       |

| 4–14           | Imperfect Filtering Setup Frame Format                 | 4-25       |

| 4–14<br>5–1    | Slave Read Cycle                                       |            |

| 5–1<br>5–2     | Slave Write Cycle                                      | 5-5        |

| 5–2<br>5–3     | Configuration Read Cycle                               | 5–5<br>5–6 |

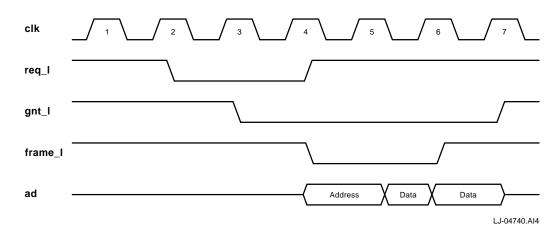

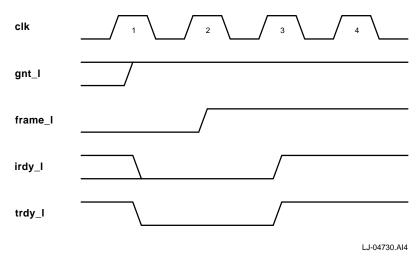

| 5–3<br>5–4     | Bus Arbitration                                        | 5–0<br>5–7 |

| J <del>-</del> |                                                        | 5-1        |

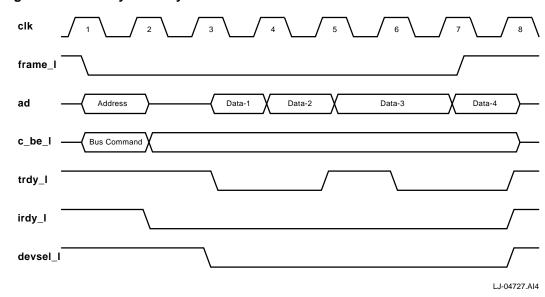

| 5–5  | Memory Read Cycle                                      | 5–8  |

|------|--------------------------------------------------------|------|

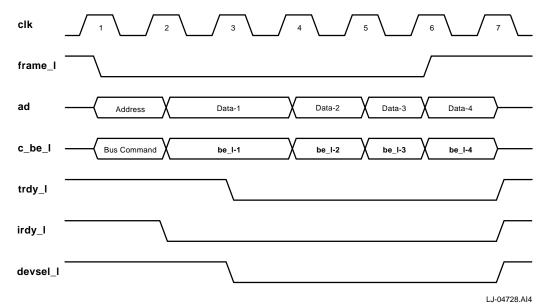

| 5–6  | Memory Write                                           | 5–9  |

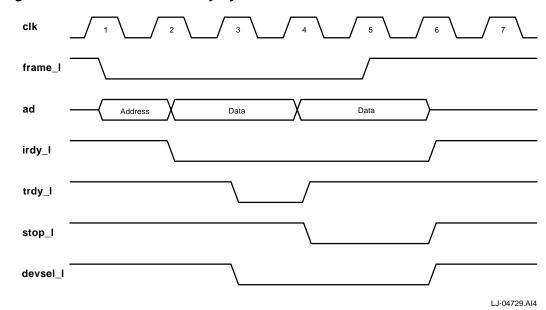

| 5–7  | 21140A-Initiated Retry Cycle                           | 5–10 |

| 5–8  | Normal Completion                                      | 5–11 |

| 5–9  | Master Abort                                           | 5–12 |

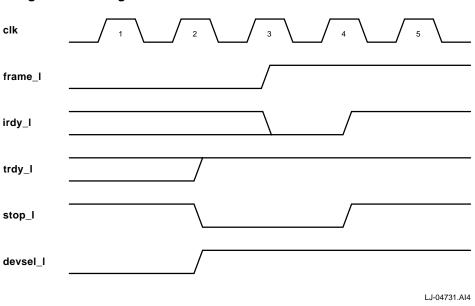

| 5–10 | Target Abort                                           | 5–13 |

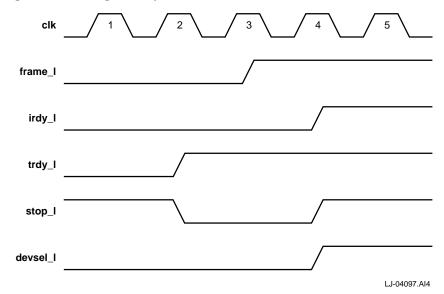

| 5–11 | Target Disconnect.                                     | 5–14 |

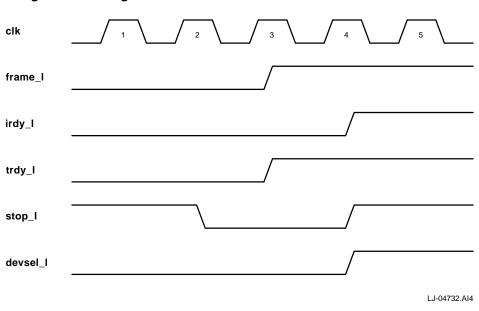

| 5–12 | Target Retry                                           | 5–15 |

| 5–13 | Parity Operation                                       | 5–16 |

| 6–1  | Ethernet Frame Format.                                 | 6–8  |

| 6–2  | Preamble Recognition Sequence in SRL Mode              | 6–16 |

| 7–1  | Boot ROM, Serial ROM, and External Register Connection | 7–2  |

| 7–2  | Boot ROM Byte Read Cycle                               | 7–4  |

| 7–3  | Boot ROM Byte Write Cycle                              | 7–5  |

| 7–4  | Boot ROM Dword Read Cycle                              | 7–6  |

| 7–5  | Read Cycle (Page 1 of 2)                               | 7–8  |

| 7–6  | Read Cycle (Page 2 of 2)                               | 7–9  |

| 7–7  | Read Operation.                                        | 7–10 |

| 7–8  | Write Cycle (Page 1 of 2)                              | 7–11 |

| 7–9  | Write Cycle (Page 2 of 2)                              | 7–12 |

| 7–10 | Write Operation                                        | 7–13 |

### Tables

| 2–1  | Functional Description of 21140A Signals                     | 2–4  |

|------|--------------------------------------------------------------|------|

| 3–1  | Configuration Registers Mapping                              | 3–2  |

| 3–2  | CFID Configuration ID Register Description                   | 3–3  |

| 3–3  | CFID Access Rules.                                           | 3–3  |

| 3–4  | CFCS Command and Status Configuration Register Description   | 3–4  |

| 3–5  | CFSC Access Rules                                            | 3–6  |

| 3–6  | CFRV Configuration Revision Register Description             | 3–7  |

| 3–7  | 21140A Revision and Step Number                              | 3–7  |

| 3–8  | CFRV Access Rules                                            | 3–8  |

| 3–9  | CFLT Configuration Latency Timer Register Description        | 3–9  |

| 3–10 | CFLT Access Rules                                            | 3–9  |

| 3–11 | CBIO Configuration Base I/O Address Register Description     | 3–10 |

| 3–12 | CBIO Access Rules                                            | 3–10 |

| 3–13 | CBMA Configuration Base Memory Address Register Description. | 3–11 |

| 3–14 | CBMA Access Rules.                                           | 3–11 |

| 3–15 | SSID Subsystem ID Register Description                       | 3–12 |

| 3–16 | SSID Access Rules.                                           | 3–12 |

| 3–17 | CBER Expansion ROM Base Address Register Description         | 3–13 |

| 3–18 | CBER Access Rules                                            | 3–13 |

| 3–19 | CFIT Configuration Interrupt Register Description            | 3–14 |

| 3–20 | CFIT Access Rules                                            | 3–15 |

| 3–21 | CFDD Configuration Driver Area Register Description          | 3–16 |

| 3–22 | CFDD Access Rules                                            | 3–16 |

| 3–23 | CSR Mapping                                                  | 3–17 |

| 3–24 | CSR0 Bus Mode Register Description                           | 3–19 |

| 3–25 | Transmit Automatic Polling Intervals.                        | 3–21 |

| 3–26 | CSR0 Access Rules                                            | 3-22 |

| 3–27 | Cache Alignment Bits                                         | 3–22 |

| 3–28 | CSR1 Transmit Poll Demand Register Description               | 3–23 |

| 3–29 | CSR1 Access Rules                                            | 3–23 |

| 3–30 | CSR2 Receive Poll Demand Register Description.               | 3–23 |

| 3–31 | CSR2 Access Rules                                            | 3–24 |

| 3–32 | CSR3 Receive List Base Address Register Description          | 3–24 |

| 3–33 | CSR3 Access Rules                                            | 3–25 |

| 3–34 | CSR4 Transmit List Base Address Register Description         | 3–25 |

| 3–35 | CSR4 Access Rules                                            | 3–25 |

| 3–36 | CSR5 Status Register Description                             | 3–27 |

| 3–37 | Fatal Bus Error Bits.                                        | 3–29 |

| 3–38 | Transmit Process State.                                      | 3-30 |

| 3–39 | Receive Process State                                        | 3–30 |

| 3–40 | CSR5 Access Rules                                            | 3–31 |

| 3–41 | CSR6 Operating Mode Register Description                     | 3–33 |

| 3–42 | Transmit Threshold                                           | 3–38 |

| 3–43 | Port and Data Rate Selection                                 | 3–38 |

|      |                                                              |      |

| 3–44       | Loopback Operation                                                | 3–39 |

|------------|-------------------------------------------------------------------|------|

| 3–45       | Filtering Mode                                                    | 3–39 |

| 3–46       | CSR6 Access Rules                                                 | 3–40 |

| 3–47       | CSR7 Interrupt Enable Register Description.                       | 3–42 |

| 3–48       | CSR7 Access Rules                                                 | 3–44 |

| 3–49       | CSR8 Missed Frames and Overflow Counter Description               | 3–45 |

| 3–50       | CSR8 Access Rules                                                 | 3–45 |

| 3–51       | CSR9 Boot ROM, Serial ROM, and MII Management RegisterDescription | 3–46 |

| 3–52       | CSR9 Access Rules                                                 | 3–48 |

| 3–53       | CSR10 Boot ROM Programming Address Description                    | 3–49 |

| 3–54       | CSR10 Access Rules                                                | 3–49 |

| 3–55       | CSR11 General-Purpose Timer Register Description.                 | 3–50 |

| 3–56       | CSR11 Access Rules                                                | 3–50 |

| 3–57       | CSR12 General-Purpose Port Register Description                   | 3–51 |

| 3–58       | CSR12 Access Rules                                                | 3–52 |

| 3–59       | CSR15 Watchdog Timer Register Description                         | 3–53 |

| 3–60       | CSR15 Access Rules                                                | 3–54 |

| 4–1        | RDES0 Receive Descriptor 0 Description.                           | 4–5  |

| 4–2        | RDES1 Receive Descriptor 1 Description                            | 4–9  |

| 4–3        | RDES2 Receive Descriptor 2 Description                            | 4–10 |

| 4–4        | RDES3 Receive Descriptor 3 Description                            | 4–10 |

| 4–5        | Receive Descriptor Status Validity                                | 4–11 |

| 4–6        | TDES0 Transmit Descriptor 0 Description                           | 4–14 |

| 4–7        | TDES1 Transmit Descriptor 1 Description                           | 4–16 |

| 4–8        | Filtering Type                                                    | 4–18 |

| 4–9        | TDES2 Transmit Descriptor 2 Description                           | 4–19 |

| 4–10       | TDES3 Transmit Descriptor 3 Description                           | 4–19 |

| 4–11       | Transmit Descriptor Status Validity                               | 4–20 |

| 4–12       | Arbitration Scheme                                                | 4-32 |

| 4–13       | Receive Process State Transitions                                 | 4-36 |

| 4–14       | Transmit Process State Transitions                                | 4-39 |

| 5–1        | Bus Commands                                                      | 5-2  |

| 6–1        | IEEE 802.3 and MII/SYM Signals                                    | 6–3  |

| 6–2        | Ethernet Frame Format.                                            | 6–8  |

| 6–3        | Frame Format                                                      | 6–9  |

| 6–4        | Ethernet Receive Address Groups                                   | 6–10 |

| 6–5        | Transmit Parameter Values                                         | 6–14 |

| 6–6        | Destination Address Bit 1                                         | 6–17 |

| 6–7        | Capture-Effect Sequence                                           | 6-21 |

| 6–8        | 2–0 Backoff Algorithm                                             | 6-22 |

| 7–1        | LED Connection                                                    | 7–14 |

| / 1<br>A–1 | JTAG Test Logic Connection Requirements.                          | A-1  |

| A-2        | Instruction Register                                              | A-3  |

| B–1        | CSMA/CD Counters                                                  | B-1  |

|            |                                                                   |      |

## Preface

### **Purpose and Audience**

The *DIGITAL Semiconductor 21140A PCI Fast Ethernet LAN Controller Hardware Reference Manual* describes the operation of the DIGITAL Semiconductor 21140A PCI Fast Ethernet LAN Controller (also referred to as the 21140A). This manual is for designers who use the 21140A.

## **Manual Organization**

This manual contains seven chapters, four appendixes, and an index.

- Chapter 1, Introduction, includes a general description of the 21140A. It also provides an overview of the 21140A hardware components.

- Chapter 2, Signal Descriptions, provides the physical layout of the 21140A and describes each of the input and output signals.

- Chapter 3, Registers, provides a complete bit description of the 21140A control and status registers (CSRs) and the configuration registers.

- Chapter 4, Host Communication, describes how the 21140A communicates with the host by using descriptor lists and data buffers. It also describes the transmit and receive processes.

- Chapter 5, Host Bus Operation, provides a description of the read, write, and termination cycles.

- Chapter 6, Network Interface Operation, describes the MII/SYM port and serial port interfaces. It includes a complete description of media access control (MAC) operations. It also provides detailed transmitting and receiving operation information.

- Chapter 7, External Ports, describes the interface and operation of the MicroWire serial ROM, the boot ROM, the general-purpose port, and the network activity LEDs.

- Appendix A, Joint Test Action Group—Test Logic, provides descriptions of the testing, the observing, and the modifying of circuit activity during normal operation.

- Appendix B, DNA CSMA/CD Counters and Events Support, describes features that support the driver in implementing and reporting the specified counters and events.

- Appendix C, Hash C Routine, provides an example of a C routine that generates a hash index for a given Ethernet address.

- Appendix D, Support, Products, and Documentation, contains technical support and ordering information.

### **Document Conventions**

The values 1, 0, and X are used in some tables. X signifies a don't care (1 or 0) state, which can be determined by the system designer.

# 1 Introduction

This chapter provides a general description of the 21140A and its features. The chapter also includes an overview of the 21140A hardware components.

## **1.1 General Description**

The 21140A is a fast Ethernet LAN controller for both 100-Mb/s and 10-Mb/s data rates, which provides a direct interface to the peripheral component interconnect (PCI) local bus. The 21140A interfaces to the host processor by using onchip control and status registers (CSRs) and a shared host memory area, set up mainly during initialization. This minimizes processor involvement in the 21140A operation during normal reception and transmission. Large FIFOs allow the 21140A to efficiently operate in systems with longer latency periods. Bus traffic is also minimized by filtering out received runt frames and by automatically retransmitting collided frames without a repeated fetch from the host memory.

The 21140A provides two network ports: a 10-Mb/s port and a 10/100-Mb/s port. The 10-Mb/s port provides a conventional 7-wire interface for the existing 10-Mb/s front-end decoder (ENDEC).

The 10/100-Mb/s port can be programmed to support various levels of interconnect. It can be programmed to support either full media-independent interface (MII) functionality or 100BASE-X physical coding sublayer (PCS), which includes 4B/5B encoder/decoder, framer, and scrambler/descrambler.

The 21140A can sustain transmission or reception of minimal-sized back-to-back packets at full line speed with an interpacket gap (IPG) of 9.6  $\mu$ s for 10 Mb/s and 0.96  $\mu$ s for 100 Mb/s. The 21140A has several additional features that are not available on the 21140, yet it remains pin and software compatible with the 21140.

### 1.1.1 21140A Features

All 21140A devices have the following features:

- Offers a single-chip Fast Ethernet controller for PCI local bus:

- Provides a glueless connection to the PCI bus

- Supports two network ports: 10 Mb/s and 10/100 Mb/s

- Provides a standard 10/100-Mb/s MII supporting CAT3 unshielded twisted-pair (UTP), CAT5 UTP, shielded twisted-pair (STP) and fiber cables

- Contains onchip scrambler and PCS for CAT5 to significantly reduce cost of 100BASE-T solutions

- Supports full-duplex operation on both 10-Mb/s and 10/100-Mb/s ports

- Provides external and internal loopback capability on both ports

- Contains a variety of flexible address filtering modes (including perfect, hash tables, inverse perfect, and promiscuous):

- 16 perfect addresses (normal or inverse filtering)

- 512 hash-filtered addresses

- 512 hash-filtered multicast addresses and one perfect address

- Pass all multicast

- Promiscuous

- Pass all incoming packets with a status report

- Offers a unique, patented solution to Ethernet capture-effect problem

- Contains large independent receive and transmit FIFOs; no additional onboard memory required

- Includes a powerful onchip direct memory access (DMA) with programmable burst size providing for low CPU utilization

- Implements unique, patent-pending intelligent arbitration between DMA channels preventing underflow or overflow

- Supports PCI clock frequency from dc to 33 MHz; network operational with PCI clock from 20 MHz to 33 MHz

- Supports an unlimited PCI burst

- Supports PCI read multiple commands

- Supports early interrupts on transmit and receive for improved performance

- Implements low-power management with two power-saving modes (sleep or snooze)

- Supports both PCI 5.0-V and 3.3-V signaling environments

- Supports either big or little endian byte ordering for buffers and descriptors

- Contains 8-bit, general-purpose, programmable register and corresponding I/O pins

- Provides LED support for various network activity indications

- Provides MicroWire interface for serial ROM (1K and 4K EEPROM)

- Provides an upgradable boot ROM interface of up to 256KB

- Supports automatic loading of sub-system vendor ID and sub-system ID from the serial ROM to the configuration register

- Implements JTAG-compatible test-access port with boundary-scan pins

- Supports IEEE 802.3, ANSI 8802-3, and Ethernet standards

- Implements low-power, 3.3-V complementary metal-oxide semiconductor (CMOS) process technology

- Supports PCI write and invalidate, and read line commands

### **1.2 Hardware Overview**

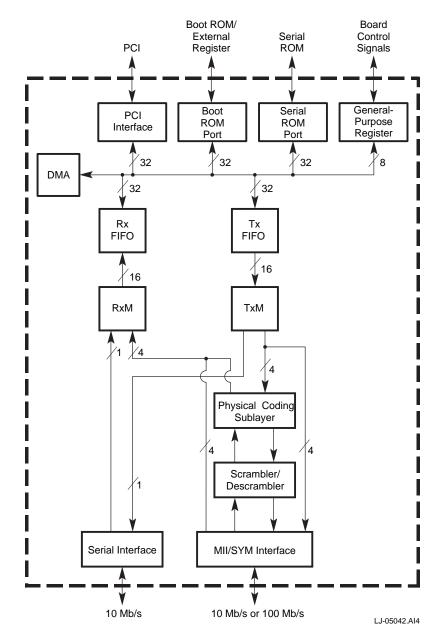

The following list describes the 21140A hardware components, and Figure 1–1 shows a block diagram of the 21140A:

- PCI interface—Includes all interface functions to the PCI bus; handles all interconnect control signals; and executes PCI DMA and I/O transactions.

- DMA—Contains dual receive and transmit controller; handles data transfers between CPU memory and onchip memory.

- FIFOs—Contains two FIFOs for receive and transmit; supports automatic packet deletion on receive (runt packets or after a collision) and packet retransmission after a collision on transmit.

### **Hardware Overview**

- TxM—Handles all CSMA/CD<sup>1</sup> MAC<sup>2</sup> transmit operations, and transfers data from transmit FIFO to the ENDEC for transmission.

- RxM—Handles all CSMA/CD receive operations, and transfers the data from the ENDEC to the receive FIFO.

- Physical coding sublayer—Implements the encoding and decoding sublayer of the 100BASE-TX (CAT5) specification, including the squelch.

- Scrambler/descrambler—Implements the twisted-pair physical layer medium dependent (TP-PMD) scrambler/descrambler scheme.

- General-purpose register—Enables software to use for input or output functions.

- Serial interface—Provides a 7-wire conventional interface to the Ethernet ENDEC components.

- MII/SYM interface—Provides a full MII signal interface and a direct interface to the 10/100-Mb/s ENDEC for CAT5.

- Serial ROM port—Provides a direct interface to the MicroWire ROM for storage of the Ethernet address and system parameters.

- Boot ROM port—Provides an interface to perform read and write operations to the boot ROM; supports accesses to bytes or longwords (32-bit). Also provides the ability to connect an external 8-bit register to the boot ROM port.

<sup>&</sup>lt;sup>1</sup>Carrier-sense multiple access with collision detection

<sup>&</sup>lt;sup>2</sup>Media access control

#### Figure 1–1 21140A Block Diagram

This chapter provides the 21140A pinout, and a functional description of each of the signals.

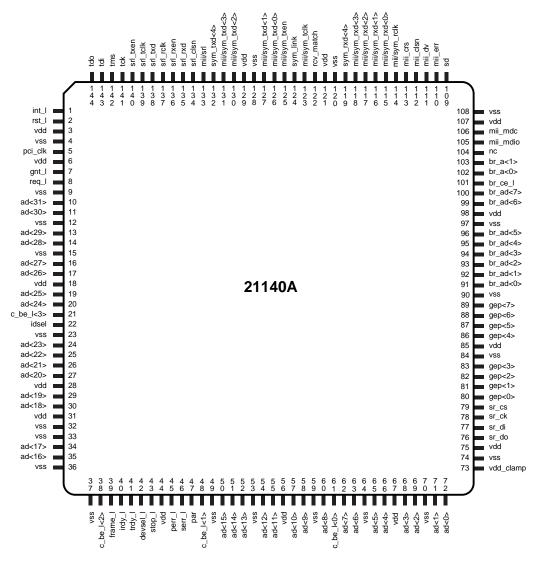

### 2.1 21140A Pinout

The 21140A is housed in the 144-pin PQFP. Figure 2–1 shows the 21140A pinout.

#### Figure 2–1 21140A Pinout Diagram (Top View)

LJ-04479.AI4

Table 2–1 provides a functional description of each of the 21140A signals.

The following terms describe the 21140A pinout:

• Address phase

Address and appropriate bus commands are driven during this cycle.

• Data phase

Data and the appropriate byte enable codes are driven during this cycle.

• \_l

All pin names with the \_l suffix are asserted low.

• The following pins have an internal pull-up resistor:

```

br_ce_l

sr_do

tdi

tms

```

• The **sr\_cs** pin has an internal pull-down resistor.

The following abbreviations are used in Table 2–1.

```

I = Input

O = Output

I/O = Input/output

O/D = Open drain

P = Power

```

| Fable 2–1 Functional Description of 21140A Signals         (Sheet 1 of) |      |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|-------------------------------------------------------------------------|------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Signal                                                                  | Туре | Pin<br>Number      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| ad<31:0>                                                                | I/O  | See<br>Figure 2–1. | 32-bit PCI address and data lines. Address and<br>data bits are multiplexed on the same pins.<br>During the first clock cycle of a transaction, the<br>address bits contain a physical address<br>(32 bits). During subsequent clock cycles,<br>these same lines contain data (32 bits). A<br>21140A bus transaction consists of an address<br>phase followed by one or more data phases.<br>The 21140A supports both read and write<br>bursts (in master operation only). Little and big<br>endian byte ordering can be used. |  |

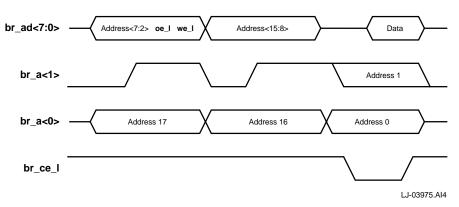

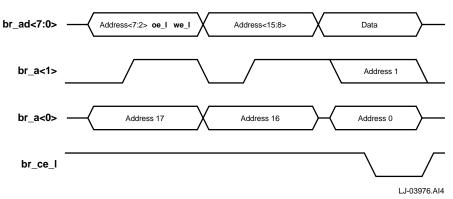

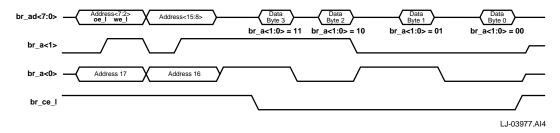

| br_a<0>                                                                 | 0    | 102                | Boot ROM address line bit 0. In a 256KB configuration, this pin also carries in two consecutive address cycles, boot ROM address bits 16 and 17.                                                                                                                                                                                                                                                                                                                                                                               |  |

| br_a<1>                                                                 | 0    | 103                | Boot ROM address line bit 1. This pin also<br>latches the boot ROM address and control lines<br>by the two external latches.                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| br_ad<7:0>                                                              | I/O  | See<br>Figure 2–1. | Boot ROM address and data multiplexed lines<br>bits 7 through 0. In the first of two consecutive<br>address cycles, these lines contain the boot<br>ROM address bits 7 through 2, <b>oe_l</b> and <b>we_l</b> ;<br>followed by boot ROM address bits 15 through<br>8 in the second cycle. During the data cycle,<br>bits 7 through 0 contain data. During operation<br>with the external register, these lines are used<br>to carry data bits 7 through 0 to and from the<br>external register.                                |  |

| br_ce_l                                                                 | 0    | 101                | Boot ROM or external register chip enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

Table 2–1 Functional Description of 21140A Signals

| Signal      | Туре | Pin<br>Number      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| c_be_l<3:0> | I/O  | See<br>Figure 2–1. | Bits 0 through 3 of the bus command and byte<br>enable lines. Bus command and byte enable<br>are multiplexed on the same PCI pins.                                                                                                                                                                                                                                                                                                             |

|             |      |                    | During the address phase of the transaction, these 4 bits provide the bus command.                                                                                                                                                                                                                                                                                                                                                             |

|             |      |                    | During the data phase, these 4 bits provide the byte enable. The byte enable determines which byte lines carry valid data. For example, bit 0 applies to byte 0, and bit 3 applies to bit 3.                                                                                                                                                                                                                                                   |

| devsel_l    | I/O  | 42                 | Device select is asserted by the target of the current bus access. When the 21140A is the initiator of the current bus access, it expects the target to assert <b>devsel_l</b> within 5 bus cycles, confirming the access. If the target does not assert <b>devsel_l</b> within the required bus cycles, the 21140A aborts the cycle. To meet the timing requirements, the 21140A asserts this signal in a medium speed (within 2 bus cycles). |

| frame_l     | I/O  | 39                 | The signal <b>frame_l</b> is driven by the 21140A<br>(bus master) to indicate the beginning and<br>duration of an access. Signal <b>frame_l</b> asserts<br>to indicate the beginning of a bus transaction.<br>While <b>frame_l</b> is asserted, data transfers<br>continue. Signal <b>frame_l</b> deasserts to indicate<br>that the next data phase is the final data phase<br>transaction.                                                    |

| gep<7:0>    | I/O  | See<br>Figure 2–1. | General-purpose pins can be used by software<br>as either status pins or control pins. These pins<br>can be configured by software to perform<br>either input or output functions.                                                                                                                                                                                                                                                             |

| gnt_l       | Ι    | 7                  | Bus grant asserts to indicate to the 21140A that access to the bus is granted.                                                                                                                                                                                                                                                                                                                                                                 |

| idsel       | Ι    | 22                 | Initialization device select asserts to indicate that the host is issuing a configuration cycle to the 21140A.                                                                                                                                                                                                                                                                                                                                 |

### Table 2–1 Functional Description of 21140A Signals

(Sheet 2 of 9)

| Signal   | Туре | Pin<br>Number | Description                                                                                                                                                                                                                                                                  |

|----------|------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| int_l    | O/D  | 1             | Interrupt request asserts when one of the<br>appropriate bits of CSR5 sets and causes an<br>interrupt, provided that the corresponding<br>mask bit in CSR7 is not asserted. Interrupt<br>request deasserts by writing a 1 into the<br>appropriate CSR5 bit.                  |

|          |      |               | If more than one interrupt bit is asserted in CSR5 and the host does not clear all input bits, the 21140A deasserts <b>int_l</b> for one cycle to support edge-triggered systems.                                                                                            |

|          |      |               | This pin must be pulled up by an external resistor.                                                                                                                                                                                                                          |

| irdy_l   | I/O  | 40            | Initiator ready indicates the bus master's ability<br>to complete the current data phase of the<br>transaction.                                                                                                                                                              |

|          |      |               | A data phase is completed on any rising edge<br>of the clock when both <b>irdy_l</b> and target ready<br><b>trdy_l</b> are asserted. Wait cycles are inserted<br>until both <b>irdy_l</b> and <b>trdy_l</b> are asserted<br>together.                                        |

|          |      |               | When the 21140A is the bus master, <b>irdy_l</b> is<br>asserted during write operations to indicate that<br>valid data is present on the 32-bit <b>ad</b> lines.<br>During read operations, the 21140A asserts<br><b>irdy_l</b> to indicate that it is ready to accept data. |

| mii_clsn | Ι    | 112           | Collision detected is asserted when detected by<br>an external physical layer protocol (PHY)<br>device.                                                                                                                                                                      |

| mii_crs  | Ι    | 113           | Carrier sense is asserted by the PHY when the media is active.                                                                                                                                                                                                               |

| mii_dv   | Ι    | 111           | Data valid is asserted by an external PHY when<br>receive data is present on the <b>mii/sym_rxd</b><br>lines and is deasserted at the end of the packet.<br>This signal should be synchronized with the<br><b>mii/sym_rclk</b> signal.                                       |

Table 2–1 Functional Description of 21140A Signals

(Sheet 3 of 9)

| Signal           | Туре | Pin<br>Number      | Description                                                                                                                                                                                                                                                                                                                                             |

|------------------|------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| mii_err          | I    | 110                | Receive error asserts when a data decoding<br>error is detected by an external PHY device.<br>This signal is synchronized to <b>mii/sym_rclk</b><br>and can be asserted for a minimum of one<br>receive clock. When asserted during a packet<br>reception, it sets the cyclic redundancy check<br>(CRC) error bit in the receive descriptor<br>(RDES0). |

| mii_mdc          | 0    | 106                | MII management data clock is sourced by the 21140A to the PHY devices as a timing reference for the transfer of information on the <b>mii_mdio</b> signal.                                                                                                                                                                                              |

| mii_mdio         | I/O  | 105                | MII management data input/output transfers<br>control information and status between the<br>PHY and the 21140A.                                                                                                                                                                                                                                         |

| mii/srl          | 0    | 133                | Indicates the selected port: SRL or MII/SYM.<br>When asserted, the MII/SYM port is active.<br>When deasserted, the SRL port is active.                                                                                                                                                                                                                  |

| mii/sym_rclk     | Ι    | 114                | Supports either the 25-MHz or 2.5-MHz receive clock. This clock is recovered by the PHY.                                                                                                                                                                                                                                                                |

| mii/sym_rxd<3:0> | Ι    | See<br>Figure 2–1. | Four parallel receive data lines when MII mode<br>is selected. This data is driven by an external<br>PHY that attached the media and should be<br>synchronized with the <b>mii/sym_rclk</b> signal.                                                                                                                                                     |

| mii/sym_tclk     | Ι    | 123                | Supports the 25-MHz or 2.5-MHz transmit<br>clock supplied by the external physical layer<br>medium dependent (PMD) device. This clock<br>should always be active.                                                                                                                                                                                       |

| mii/sym_txd<3:0> | 0    | See<br>Figure 2–1. | Four parallel transmit data lines. This data is<br>synchronized to the assertion of the<br><b>mii/sym_tclk</b> signal and is latched by the<br>external PHY on the rising edge of the<br><b>mii/sym_tclk</b> signal.                                                                                                                                    |

### Table 2–1 Functional Description of 21140A Signals

(Sheet 4 of 9)

| Signal    | Туре | Pin<br>Number | Description                                                                                                                                                                                                                                                                                                             |

|-----------|------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| mii_txen  | 0    | 125           | Transmit enable signals that the transmit is<br>active to an external PHY device. In PCS<br>mode CSR6<23>, this signal reflects the<br>transmit activity of the MAC sublayer.                                                                                                                                           |

| nc        | 0    | 104           | No connection.                                                                                                                                                                                                                                                                                                          |

| par       | I/O  | 47            | Parity is calculated by the 21140A as an even parity bit for the 32-bit <b>ad</b> and 4-bit <b>c_be_l</b> lines.                                                                                                                                                                                                        |

|           |      |               | During address and data phases, parity is calculated on all the <b>ad</b> and <b>c_be_l</b> lines whether or not any of these lines carry meaningful information.                                                                                                                                                       |

| pci_clk   | Ι    | 5             | The clock provides the timing for the 21140A related PCI bus transactions. All the bus signals are sampled on the rising edge of <b>pci_clk</b> . The clock frequency range is between 25 MHz and 33 MHz.                                                                                                               |

| perr_l    | I/O  | 45            | Parity error asserts when a data parity error is detected.                                                                                                                                                                                                                                                              |

|           |      |               | When the 21140A is the bus master and a parity error is detected, the 21140A asserts both CSR5 bit 13 (system error) and CFCS bit 24 (Data Parity Report). Next, it completes the current data burst transaction, and then stops operation. After the host clears the system error, the 21140A continues its operation. |

|           |      |               | The 21140A asserts <b>perr_l</b> when a data parity error is detected in either master-read or slave-write operations.                                                                                                                                                                                                  |

|           |      |               | This pin must be pulled up by an external resistor.                                                                                                                                                                                                                                                                     |

| rcv_match | Ο    | 122           | Receive match indication is asserted when a received packet has passed address recognition.                                                                                                                                                                                                                             |

### Table 2–1 Functional Description of 21140A Signals

(Sheet 5 of 9)

| Signal   | Туре | Pin<br>Number | Description                                                                                                                                                                                                                        |

|----------|------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| req_l    | 0    | 8             | Bus request is asserted by the 21140A to indicate to the bus arbiter that it wants to use the bus.                                                                                                                                 |

| rst_l    | Ι    | 2             | Resets the 21140A to its initial state. This signal must be asserted for at least 10 active PCI clock cycles. When in the reset state, all PCI output pins are put into tristate and all PCI open drain (O/D) signals are floated. |

| sd       | Ι    | 109           | Signal detect indication supplied by an external physical layer medium dependent (PMD) device.                                                                                                                                     |

| serr_l   | O/D  | 46            | If an address parity error is detected while<br>CFCS bit 8 (serr_l enable) is enabled, the<br>21140A asserts both serr_l (system error) and<br>CFCS bit 30 (signal system error).                                                  |

|          |      |               | When an address parity error is detected,<br>system error asserts two clock cycles after the<br>failing address.                                                                                                                   |

|          |      |               | This pin must be pulled up by an external resistor.                                                                                                                                                                                |

| sr_ck    | 0    | 78            | Serial ROM clock signal.                                                                                                                                                                                                           |

| sr_cs    | 0    | 79            | Serial ROM chip-select signal.                                                                                                                                                                                                     |

| sr_di    | 0    | 77            | Serial ROM data-in signal.                                                                                                                                                                                                         |

| sr_do    | Ι    | 76            | Serial ROM data-out signal.                                                                                                                                                                                                        |

| srl_clsn | Ι    | 134           | Collision detect signals a collision occurrence<br>on the Ethernet cable to the 21140A. It may be<br>asserted and deasserted asynchronously by the<br>external ENDEC to the receive clock.                                         |

| srl_rclk | Ι    | 137           | Receive clock carries the recovered receive clock supplied by an external ENDEC. During idle periods, <b>srl_rclk</b> may be inactive.                                                                                             |

### Table 2–1 Functional Description of 21140A Signals

(Sheet 6 of 9)

| Signal     | Туре | Pin<br>Number | Description                                                                                                                                                                                                                                                                                              |

|------------|------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| srl_rxd    | Ι    | 135           | Receive data carries the input receive data from<br>the external ENDEC. The incoming data<br>should be synchronous with the <b>srl_rclk</b><br>signal.                                                                                                                                                   |

| srl_rxen   | Ι    | 136           | Receive enable signals activity on the Ethernet cable to the 21140A. It is asserted when receive data is present on the Ethernet cable and deasserted at the end of a frame. It may be asserted and deasserted asynchronously to the receive clock ( <b>srl_rclk</b> ) by the external ENDEC.            |

| srl_tclk   | Ι    | 139           | Transmit clock carries the transmit clock<br>supplied by an external ENDEC. This clock<br>must always be active (even during reset).                                                                                                                                                                     |

| srl_txd    | 0    | 138           | Transmit data carries the serial output data from the 21140A. This data is synchronized to the <b>srl_tclk</b> signal.                                                                                                                                                                                   |

| srl_txen   | 0    | 140           | Transmit enable signals an external ENDEC that the 21140A transmit is in progress.                                                                                                                                                                                                                       |

| stop_l     | I/O  | 43            | Stop indicator indicates that the current target<br>is requesting the bus master to stop the current<br>transaction.                                                                                                                                                                                     |

|            |      |               | The 21140A responds to the assertion of <b>stop_l</b> when it is the bus master, either to disconnect, retry, or abort.                                                                                                                                                                                  |

| sym_link   | 0    | 124           | Indicates that the descrambler is locked to the input data signal.                                                                                                                                                                                                                                       |

| sym_rxd<4> | Ι    | 119           | Receive data together with the four receive<br>lines <b>mii/sym_rxd&lt;3:0&gt;</b> provide five parallel<br>lines of data in symbol form for use in PCS<br>mode (100BASE-T, CSR6<23>). This data is<br>driven by an external PMD device and should<br>be synchronized to the <b>mii/sym_rclk</b> signal. |

### Table 2–1 Functional Description of 21140A Signals

(Sheet 7 of 9)

| Signal     | Туре | Pin<br>Number | Description                                                                                                                                                                                                                                                           |  |

|------------|------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| sym_txd<4> | 0    | 132           | Transmit data together with the four transmit<br>lines <b>mii/sym_txd&lt;3:0&gt;</b> provide five parallel<br>lines of data in symbol form for use in PCS<br>mode (100BASE-T, CSR6<23>). This data is<br>synchronized on the rising of the <b>sym_tclk</b><br>signal. |  |

| tck        | Ι    | 141           | JTAG clock shifts state information and test data into and out of the 21140A during JTAG test operations. This pin should not be left unconnected.                                                                                                                    |  |

| tdi        | Ι    | 143           | JTAG data-in pin is used to serially shift test<br>data and instructions into the 21140A during<br>JTAG test operations.                                                                                                                                              |  |

| tdo        | 0    | 144           | JTAG data-out pin is used to serially shift test<br>data and instructions out of the 21140A durin<br>JTAG test operations.                                                                                                                                            |  |

| tms        | Ι    | 142           | JTAG test mode select controls the state operation of JTAG testing in the 21140A.                                                                                                                                                                                     |  |

| trdy_l     | I/O  | 41            | Target ready indicates the target agent's ability to complete the current data phase of the transaction.                                                                                                                                                              |  |

|            |      |               | A data phase is completed on any clock when<br>both <b>trdy_l</b> and <b>irdy_l</b> are asserted. Wait<br>cycles are inserted until both <b>irdy_l</b> and <b>trdy_l</b><br>are asserted together.                                                                    |  |

|            |      |               | When the 21140A is the bus master, target<br>ready is asserted by the bus slave on the read<br>operation, indicating that valid data is present<br>on the <b>ad</b> lines. During a write cycle, it<br>indicates that the target is prepared to accept<br>data.       |  |

### Table 2–1 Functional Description of 21140A Signals

(Sheet 8 of 9)

| Signal    | Туре | Pin<br>Number      | Description                                                                                                    |

|-----------|------|--------------------|----------------------------------------------------------------------------------------------------------------|

| vdd       | Р    | See<br>Figure 2–1. | A 3.3-V supply input voltage.                                                                                  |

| vdd_clamp | Р    | 73                 | A 5-V reference for a 5-V signaling<br>environment and a 3.3-V reference for a 3.3-V<br>signaling environment. |

| VSS       | Р    | See<br>Figure 2–1. | Ground pins.                                                                                                   |

Table 2–1

Functional Description of 21140A Signals

(Sheet 9 of 9)

# 3 Registers

This chapter describes the configuration registers, and the command and status registers (CSRs) of the 21140A. The 21140A uses 10 configuration registers for initialization and configuration, and 16 CSRs (CSR0 through CSR15) for host communication. Configuration registers are used to identify and query the 21140A. The CSRs, which are mapped in the host I/O or memory address space, are used for initialization, pointers, commands, and status reporting.

**Note:** All shaded bits in the figures in this chapter are reserved and should be written by the driver as zero.

## 3.1 Configuration Operation

The 21140A enables a full software-driven initialization and configuration. This permits the software to identify and query the 21140A.

The 21140A treats configuration space write operations to registers that are reserved as no-ops. That is, the access completes normally on the bus and the data is discarded. Read accesses, to reserved or unimplemented registers, complete normally and a data value of 0 is returned.

Software reset CSR0<0> has no effect on the configuration registers. Hardware reset sets the configuration registers to their default values.

The 21140A supports byte, word, and longword accesses to configuration registers.

### **Configuration Operation**

### 3.1.1 Configuration Register Mapping

Table 3–1 lists the definitions and addresses for the configuration registers.

| Configuration Register     | Identifier | I/O Address Offset |

|----------------------------|------------|--------------------|

| Identification             | CFID       | 00H                |

| Command and status         | CFCS       | 04H                |

| Revision                   | CFRV       | 08H                |

| Latency timer              | CFLT       | 0CH                |

| Base I/O address           | CBIO       | 10H                |

| Base memory address        | CBMA       | 14H                |

| Reserved                   | _          | 18H–28H            |

| Subsystem ID               | SSID       | 2CH                |

| Expansion ROM base address | CBER       | 30H                |

| Reserved                   | _          | 34H-38H            |

| Interrupt                  | CFIT       | ЗСН                |

| Device and driver area     | CFDD       | 40H                |

Table 3–1 Configuration Registers Mapping

### 3.1.2 Configuration Registers

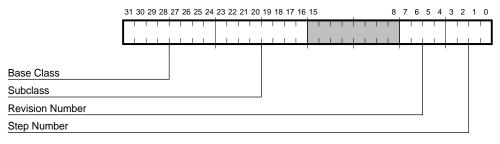

The 21140A implements 10 configuration registers. These registers are described in the following subsections.

### 3.1.2.1 Configuration ID Register (CFID–Offset 00H)

The CFID register identifies the 21140A. Figure 3–1 shows the CFID register bit fields and Table 3–2 describes the bit fields.

### Figure 3–1 CFID Configuration ID Register

| 31 30 29 28 | 27 26 25 24 | 23 22 21 20 | 19 18 17 16 | 15 14 13 12 | 11 10 9 8 7 | 654 | 3 2 1 0 |

|-------------|-------------|-------------|-------------|-------------|-------------|-----|---------|

| Device ID   |             |             | Vendor ID   |             |             |     |         |

|             |             |             |             |             |             |     |         |

LJ-04696.AI4

| Field | Description                                                           |

|-------|-----------------------------------------------------------------------|

| 31:16 | <b>Device ID</b><br>Provides the unique 21140A ID number (0009H).     |

| 15:0  | <b>Vendor ID</b><br>Specifies the manufacturer of the 21140A (1011H). |

Table 3–2 CFID Configuration ID Register Description

Table 3–3 lists the access rules for the CFID register.

| Category                   | Description            |  |

|----------------------------|------------------------|--|

| Value after hardware reset | 00091011H              |  |

| Read access rules          |                        |  |

| Write access rules         | Writing has no effect. |  |

## Table 3–3 CFID Access Rules

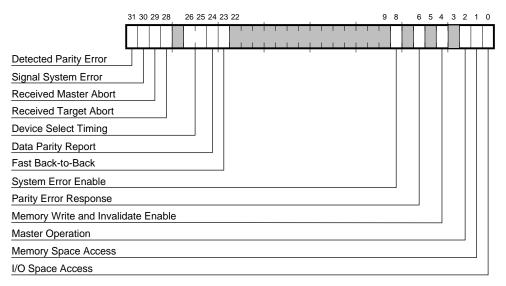

### 3.1.2.2 Command and Status Configuration Register (CFCS–Offset 04H)

The CFCS register is divided into two sections: a command register (CFCS<15:0>) and a status register (CFCS<31:16>).

The command register provides control of the 21140A's ability to generate and respond to PCI cycles. Writing 0 to this register, the 21140A logically disconnects from the PCI bus for all accesses except configuration accesses.

The status register records status information for the PCI bus-related events. The CFCS status bits do not clear when read. Writing 1 to these bits clears them; writing 0 has no effect.

Figure 3–2 shows the CFCS bit fields and Table 3–4 describes the bit fields.

# **Configuration Operation**

## Figure 3–2 CFCS Command and Status Configuration Register

LJ03932B.AI4

#### Table 3–4 CFCS Command and Status Configuration Register Description (Sheet 1 of 3)

| Field | Bit Type | Description                                                                                                                                                                      |

|-------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | Status   | <b>Detected Parity Error</b><br>When set, indicates that the 21140A detected a parity error,<br>even if parity error handling is disabled in parity error<br>response (CFCS<6>). |

| 30    | Status   | <b>Signal System Error</b><br>When set, indicates that the 21140A asserted the system<br>error ( <b>serr_l</b> ) pin.                                                            |

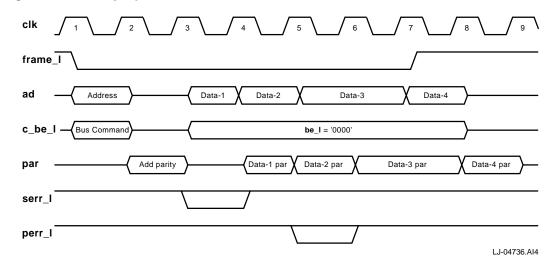

| 29    | Status   | <b>Received Master Abort</b><br>When set, indicates that the 21140A terminated a master<br>transaction with master abort.                                                        |